# MIPS32® 74K<sup>™</sup> Processor Core Family Software User's Manual

Document Number: MD00519 Revision 01.03 November 14, 2008

MIPS Technologies, Inc. 955 East Arques Avenue Sunnyvale, CA 94085-4521

Copyright © 2007, 2008 MIPS Technologies Inc. All rights reserved.

Copyright © 2007, 2008 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS-3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS-VERIFIED, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 24K, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, R3000, R4000, R5000, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, OCI, PDtrace, the Pipeline, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it, System Navigator, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

Template: nB1.03, Built with tags: 2B

# **Table of Contents**

| Chapter 1: Introduction to the MIPS32® 74K™             | 23 |

|---------------------------------------------------------|----|

| 1.1: 74K <sup>™</sup> Core Features                     |    |

| 1.1.1: Pipeline                                         | 24 |

| 1.1.2: Instruction Set                                  | 25 |

| 1.1.3: Memory Management, Caches, and Scratchpad Memory | 26 |

| 1.1.4: Interfaces                                       | 27 |

| 1.1.5: Power Control                                    | 27 |

| 1.1.6: Debug                                            | 27 |

| 1.1.7: Other                                            | 28 |

| 1.2: 74K <sup>™</sup> Core Block Diagram                | 28 |

| 1.2.1: Instruction Fetch Unit (IFU)                     | 30 |

| 1.2.2: Instruction Cache                                | 30 |

| 1.2.3: Instruction Decode/Dispatch Unit (IDU)           | 30 |

| 1.2.4: Instruction Execution Unit (IEU)                 | 31 |

| 1.2.5: Multiply Divide Unit (MDU)                       | 31 |

| 1.2.6: CorExtend® User Defined Instructions (UDIs)      |    |

| 1.2.7: Load Store Unit (LSU)                            | 32 |

| 1.2.8: System Control Coprocessor (CP0)                 | 32 |

| 1.2.9: Memory Management Unit (MMU)                     | 32 |

| 1.2.10: Data Cache                                      | 33 |

| 1.2.11: Scratchpad RAM                                  | 33 |

| 1.2.12: Graduation Unit (GRU)                           | 33 |

| 1.2.13: Bus Interface Unit (BIU)                        | 34 |

| 1.2.14: Coprocessor Interface Unit (CIU)                |    |

| 1.2.15: Power Management                                |    |

| 1.2.16: EJTAG Debug                                     | 34 |

|                                                         |    |

| Chapter 2: Pipeline of the 74K <sup>™</sup> Core        |    |

| 2.1: Integer Pipeline Description                       |    |

| 2.1.1: IFU Pipeline                                     |    |

| 2.1.1.1: IT - Instruction Cache Tag Access              |    |

| 2.1.1.2: ID - Instruction Cache Data Access             |    |

| 2.1.1.3: IS - Instruction Select                        |    |

| 2.1.1.4: IR - Instruction Recode                        |    |

| 2.1.1.5: IK - Instruction                               |    |

| 2.1.1.6: IX - Instruction Macro Expansion               |    |

| 2.1.1.7: IB - Instruction Buffer                        |    |

| 2.1.2: Instruction Decode Unit Pipeline                 |    |

| 2.1.2.1: DD - Dispatch Decode                           |    |

| 2.1.2.2: DR - Dispatch Rename                           |    |

| 2.1.2.3: DS - Dispatch Select                           |    |

| 2.1.2.4: DM - DDQ Mux                                   |    |

| 2.1.3: ALU Pipeline                                     |    |

| 2.1.3.1: AF - ALU Pipe Register File Read               |    |

| 2.1.3.2: AM - ALU Pipe Operand Bypass Select Mux        |    |

| 2.1.3.3: AC - ALU Compute                               |    |

| 2.1.3.4: AB - ALU Bypass                                | 41 |

|   | 2.1.4: MDU Pipeline                                                               | 42 |

|---|-----------------------------------------------------------------------------------|----|

|   | 2.1.4.1: MB - Multiplier Booth Recode                                             | 42 |

|   | 2.1.4.2: M1- M3 Multiplier Array                                                  |    |

|   | 2.1.4.3: M4 - Multiply Add                                                        |    |

|   | 2.1.5: AGEN Pipeline                                                              |    |

|   | 2.1.5.1: EM - Execute Operand Bypass Select Mux                                   |    |

|   | 2.1.5.2: EA - Execute and Address Generate                                        |    |

|   | 2.1.5.3: EC - Execute and Cache Access                                            |    |

|   | 2.1.5.4: ES - Execute and Cache Second                                            |    |

|   | 2.1.5.5: EB - Execute and Cache Data Bypass                                       |    |

|   | 2.1.6: GRU Pipeline                                                               |    |

|   | 2.1.6.1: WB - Writeback                                                           |    |

|   | 2.1.6.2: GC - Graduation Commit                                                   |    |

|   | 2.2: Programming the 74K Core                                                     |    |

|   | 2.3: Hazards                                                                      |    |

|   | 2.3.1: Types of Hazards                                                           |    |

|   | 2.3.1.1: Execution Hazards                                                        |    |

|   | 2.3.1.2: Instruction Hazards                                                      |    |

|   |                                                                                   |    |

|   | 2.3.2: Instruction Listing                                                        |    |

|   | 2.3.3: Eliminating Hazards                                                        |    |

|   | 2.3.3. Eliminating hazards                                                        | 47 |

| _ | hanter 2. Floating Boint Unit of the ZAKITM Core                                  | 40 |

| L | hapter 3: Floating-Point Unit of the 74Kf™ Core                                   |    |

|   | 3.1: Features Overview                                                            |    |

|   | 3.1.1: IEEE Standard 754                                                          |    |

|   | 3.2: Enabling the Floating-Point Coprocessor                                      |    |

|   | 3.3: Data Formats                                                                 |    |

|   | 3.3.1: Floating-Point Formats                                                     |    |

|   | 3.3.1.1: Normalized and Denormalized Numbers                                      |    |

|   | 3.3.1.2: Reserved Operand Values—Infinity and NaN                                 |    |

|   | 3.3.1.3: Infinity and Beyond                                                      |    |

|   | 3.3.1.4: Signalling Non-Number (SNaN)                                             |    |

|   | 3.3.1.5: Quiet Non-Number (QNaN)                                                  |    |

|   | 3.3.2: Fixed-Point Formats                                                        |    |

|   | 3.4: Floating-Point General Registers                                             |    |

|   | 3.4.1: FPRs and Formatted Operand Layout                                          |    |

|   | 3.4.2: Formats of Values Used in FP Registers                                     |    |

|   | 3.4.3: Binary Data Transfers (32-Bit and 64-Bit)                                  |    |

|   | 3.5: Floating-Point Control Registers                                             |    |

|   | 3.5.1: Floating-Point Implementation Register (FIR, CP1 Control Register 0)       |    |

|   | 3.5.2: Floating-Point Condition Codes Register (FCCR, CP1 Control Register 25)    |    |

|   | 3.5.3: Floating-Point Exceptions Register (FEXR, CP1 Control Register 26)         |    |

|   | 3.5.4: Floating-Point Enables Register (FENR, CP1 Control Register 28)            |    |

|   | 3.5.5: Floating-Point Control and Status Register (FCSR, CP1 Control Register 31) |    |

|   | 3.5.6: Operation of the FS/FO/FN Bits                                             |    |

|   | 3.5.6.1: Flush To Zero Bit                                                        |    |

|   | 3.5.6.2: Flush Override Bit                                                       |    |

|   | 3.5.6.3: Flush to Nearest                                                         |    |

|   | 3.5.6.4: Recommended FS/FO/FN Settings                                            |    |

|   | 3.5.7: FCSR Cause Bit Update Flow                                                 |    |

|   | 3.5.7.1: Exceptions Triggered by CTC1                                             |    |

|   | 3.5.7.2: Generic Flow                                                             |    |

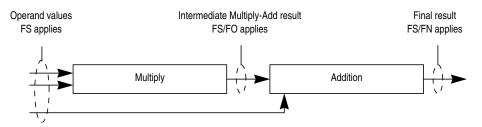

|   | 3.5.7.3: Multiply-Add Flow                                                        | 67 |

| 3.5.7.4: Cause Update Flow for Input Operands                                          | 68 |

|----------------------------------------------------------------------------------------|----|

| 3.5.7.5: Cause Update Flow for Unimplemented Operations                                | 68 |

| 3.6: Instruction Overview                                                              |    |

| 3.6.1: Data Transfer Instructions                                                      | 68 |

| 3.6.1.1: Data Alignment in Loads, Stores, and Moves                                    | 69 |

| 3.6.1.2: Addressing Used in Data Transfer Instructions                                 |    |

| 3.6.2: Arithmetic Instructions                                                         |    |

| 3.6.3: Conversion Instructions                                                         |    |

| 3.6.4: Formatted Operand-Value Move Instructions                                       |    |

| 3.6.5: Conditional Branch Instructions                                                 |    |

| 3.6.6: Miscellaneous Instructions                                                      |    |

| 3.7: Exceptions                                                                        |    |

| 3.7.1: Precise Exception Mode                                                          |    |

| 3.7.2: Exception Conditions                                                            |    |

| 3.7.2.1: Invalid Operation Exception                                                   |    |

| 3.7.2.2: Division By Zero Exception                                                    |    |

| 3.7.2.3: Underflow Exception                                                           |    |

| 3.7.2.4: Overflow Exception                                                            |    |

| 3.7.2.5: Inexact Exception                                                             |    |

| 3.7.2.6: Unimplemented Operation Exception                                             |    |

| 3.8: Pipeline and Performance                                                          |    |

| 3.8.1: Pipeline Overview                                                               |    |

| 3.8.1.1: DR Stage - Dispatch Rename                                                    |    |

| 3.8.1.2: C1 - Coprocessor Interface Unit Stage 1                                       |    |

| 3.8.1.3: CR Stage - Coprocessor Interface Unit Queue Read                              |    |

| 3.8.1.4: CI Stage - Coprocessor 1 Interface                                            |    |

| 3.8.1.5: FR Stage - Decode, Register Read, and Unpack                                  |    |

| 3.8.1.6: M1 Stage - Multiply Tree                                                      |    |

| 3.8.1.7: M2 Stage - Multiply Complete                                                  |    |

| 3.8.1.8: A1 Stage - Addition First Step                                                |    |

| 3.8.1.9: A2 Stage - Addition Second and Final Step                                     |    |

| 3.8.1.10: FP Stage - Result Pack                                                       |    |

| 3.8.1.11: FW Stage - Register Write                                                    |    |

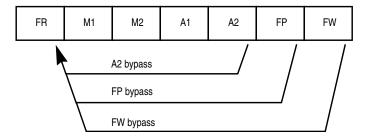

| 3.8.2: Bypassing                                                                       |    |

| 3.8.3: Repeat Rate and Latency                                                         |    |

| Chapter 4: The MIPS® DSP Application-Specific Extension to the MIPS32® Instruction Set | 81 |

| 4.1: Additional Register State for the DSP ASE                                         |    |

| 4.1.1: HI-LO Registers                                                                 |    |

| 4.1.2: DSP Control Register                                                            |    |

| 4.2: Software Detection of the DSP ASE Revision 2                                      |    |

|                                                                                        |    |

| Chapter 5: Memory Management of the 74K <sup>™</sup> Core                              |    |

| 5.1: Introduction                                                                      |    |

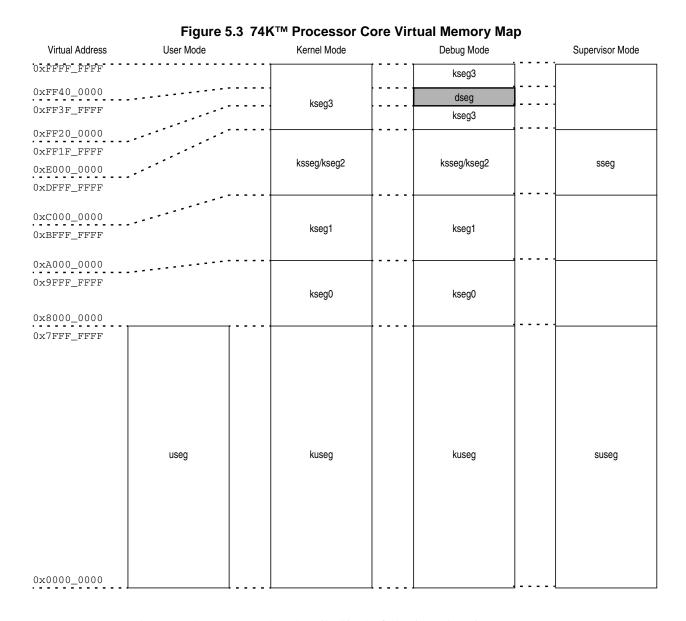

| 5.2: Modes of Operation                                                                |    |

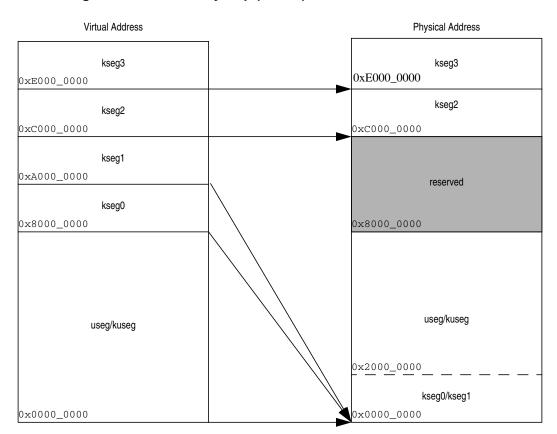

| 5.2.1: Virtual Memory Segments                                                         |    |

| 5.2.1.1: Unmapped Segments                                                             |    |

| 5.2.1.2: Mapped Segments                                                               |    |

| 5.2.2: User Mode                                                                       |    |

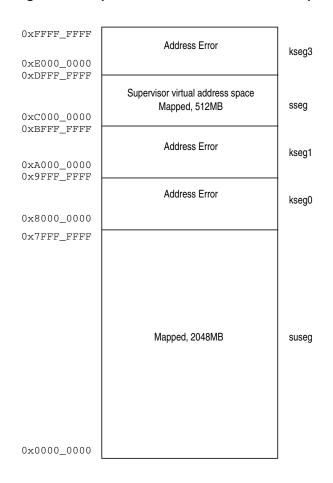

| 5.2.3: Supervisor Mode                                                                 |    |

| 5.2.4: Kernel Mode                                                                     |    |

| 5.2.4.1: Kernel Mode, User Space (kuseg)                                               |    |

| 5.2.4.2: Kernel Mode, Kernel Space 0 (kseg0)                                           | 94 |

|    | 5.2.4.3: Kernel Mode, Kernel Space 1 (kseg1)                          |      |

|----|-----------------------------------------------------------------------|------|

|    | 5.2.4.4: Kernel Mode, Kernel/Supervisor Space 2 (ksseg/kseg2)         | 95   |

|    | 5.2.4.5: Kernel Mode, Kernel Space 3 (kseg3)                          | 95   |

|    | 5.2.5: Debug Mode                                                     |      |

|    | 5.2.5.1: Debug Mode, Register (drseg)                                 |      |

|    | 5.2.5.2: Debug Mode, Memory (dmseg)                                   |      |

|    | 5.3: Translation Lookaside Buffer                                     |      |

|    | 5.3.1: Joint TLB                                                      | 97   |

|    | 5.3.2: Instruction TLB                                                |      |

|    | 5.4: Virtual-to-Physical Address Translation                          |      |

|    | 5.4.1: Hits, Misses, and Multiple Matches                             |      |

|    | 5.4.2: Memory Space                                                   |      |

|    | 5.4.2.1: Page Sizes                                                   |      |

|    | 5.4.2.2: Replacement Algorithm                                        |      |

|    | 5.4.3: TLB Instructions                                               |      |

|    | 5.5: Fixed Mapping MMU                                                | 104  |

|    |                                                                       |      |

| CI | hapter 6: Exceptions and Interrupts in the 74K™ Core                  |      |

|    | 6.1: Exception Conditions                                             |      |

|    | 6.2: Exception Priority                                               |      |

|    | 6.3: Interrupts                                                       |      |

|    | 6.3.1: Interrupt Modes                                                |      |

|    | 6.3.1.1: Interrupt Compatibility Mode                                 |      |

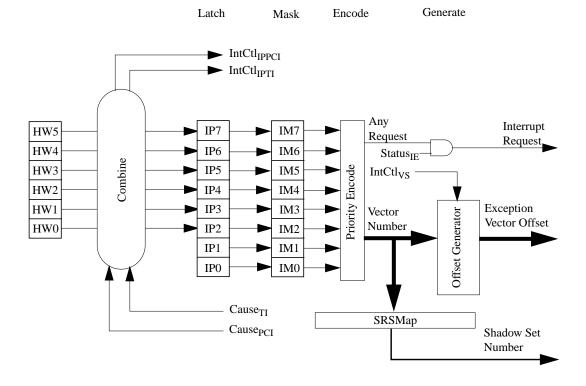

|    | 6.3.1.2: Vectored Interrupt Mode                                      |      |

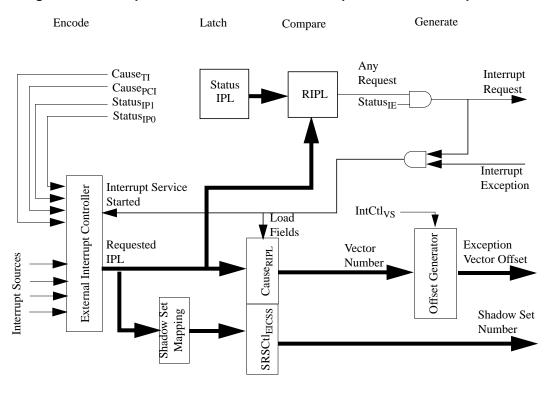

|    | 6.3.1.3: External Interrupt Controller Mode                           |      |

|    | 6.3.2: Generation of Exception Vector Offsets for Vectored Interrupts |      |

|    | 6.4: GPR Shadow Registers                                             |      |

|    | 6.5: Exception Vector Locations                                       |      |

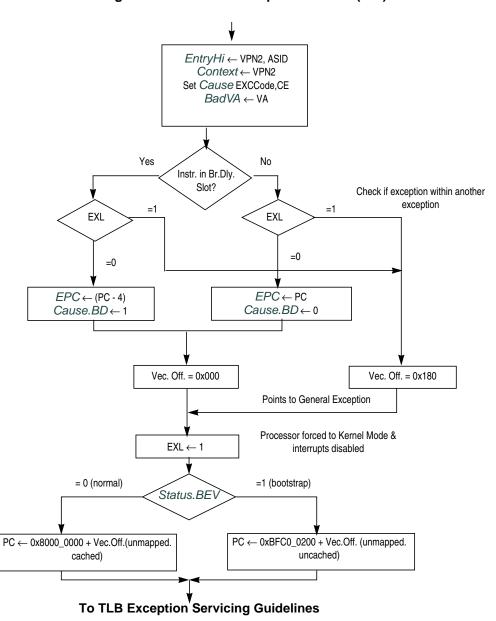

|    | 6.6: General Exception Processing                                     |      |

|    | 6.7: Debug Exception Processing                                       |      |

|    | 6.8: Exception Descriptions                                           |      |

|    | 6.8.1: Reset Exception                                                |      |

|    | 6.8.2: Debug Single Step Exception                                    |      |

|    | 6.8.3: Debug Interrupt Exception                                      |      |

|    | 6.8.4: Non-Maskable Interrupt (NMI) Exception                         |      |

|    | 6.8.5: Machine Check Exception.                                       |      |

|    | 6.8.6: Interrupt Exception                                            |      |

|    | 6.8.7: Debug Instruction Break Exception                              |      |

|    | 6.8.8: Watch Exception — Instruction Fetch or Data Access             |      |

|    | 6.8.9: Address Error Exception — Instruction Fetch/Data Access        |      |

|    | 6.8.10: TLB Refill Exception — Instruction Fetch or Data Access       |      |

|    | 6.8.11: TLB Invalid Exception — Instruction Fetch or Data Access      |      |

|    | 6.8.12: Cache Error Exception                                         |      |

|    | 6.8.13: Bus Error Exception — Instruction Fetch or Data Access        |      |

|    | 6.8.14: Debug Software Breakpoint Exception                           |      |

|    |                                                                       |      |

|    | 6.8.16: Execution Exception — Breakpoint                              |      |

|    | 6.8.18: Execution Exception — Reserved Instruction                    |      |

|    | 6.8.19: Execution Exception — Coprocessor Unusable                    |      |

|    | 6.8.20: Execution Exception — DSP ASE State Disabled                  |      |

|    | 6.8.21: Execution Exception — Floating Point Exception                |      |

|    | 6.8.22: Execution Exception — Floating Point Exception                |      |

|    | U.U.ZZ. EXECUTION EXCEPTION — INTEGENOVENION                          | 1 33 |

|    | 6.8.23: Execution Exception — Trap                                                                     | . 135 |

|----|--------------------------------------------------------------------------------------------------------|-------|

|    | 6.8.24: Debug Data Break Exception                                                                     | . 135 |

|    | 6.8.25: TLB Modified Exception — Data Access                                                           | 136   |

|    | 6.9: Exception Handling and Servicing Flowcharts                                                       | 136   |

|    |                                                                                                        |       |

| Cł | apter 7: CP0 Registers of the 74K™ Core                                                                |       |

|    | 7.1: CP0 Register Summary                                                                              | . 143 |

|    | 7.2: CP0 Register Descriptions                                                                         |       |

|    | 7.2.1: Index (CP0 Register 0, Select 0): Index into TLB array                                          |       |

|    | 7.2.2: Random (CP0 Register 1, Select 0): Randomly Generated Index into the TLB Array                  | . 149 |

|    | 7.2.3: EntryLo0-1 (CP0 Registers 2 and 3, Select 0): Output (physical) side of TLB entry               | . 149 |

|    | 7.2.4: Context (CP0 Register 4, Select 0): Mixture of Pre-programmed and BadVAddr Bits which can ac    | t as  |

|    | an OS Page Table Pointer                                                                               |       |

|    | 7.2.5: UserLocal (CP0 Register 4, Select 2): Address Causing the Last TLB-related Exception            |       |

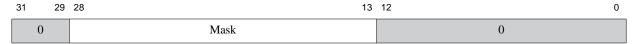

|    | 7.2.6: PageMask (CP0 Register 5, Select 0): Control for Variable Page Size in TLB Entries              |       |

|    | 7.2.7: Wired (CP0 Register 6, Select 0): Controls Number of Fixed ("wired") TLB Entries                |       |

|    | 7.2.8: HWREna (CP0 Register 7, Select 0): Bitmask Limiting User-mode Access to rdhwr Registers         | . 154 |

|    | 7.2.9: BadVAddr (CP0 Register 8, Select 0): Address Causing the Last TLB-related Exception             | . 155 |

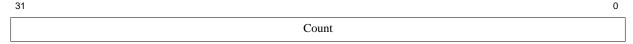

|    | 7.2.10: Count (CP0 Register 9, Select 0): Free-running Counter at Pipeline Speed                       | 155   |

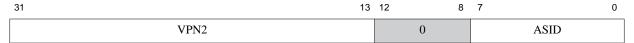

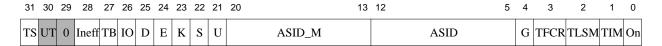

|    | 7.2.11: EntryHi (CP0 Register10, Select 0): High-order Portion of TLB Entry                            | 156   |

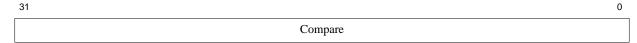

|    | 7.2.12: Compare (CP0 Register 11, Select 0): Timer Interrupt Control                                   | . 157 |

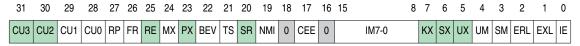

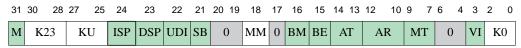

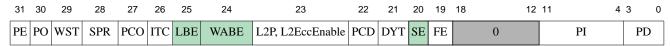

|    | 7.2.13: Status (CP0 Register 12, Select 0): Processor Status and Control                               | . 157 |

|    | 7.2.13.1: Interruptibility                                                                             |       |

|    | 7.2.13.2: Privilege Levels                                                                             |       |

|    | 7.2.13.3: Coprocessor Accessibility                                                                    |       |

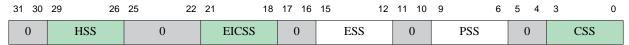

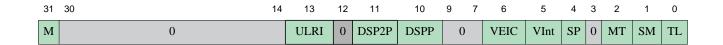

|    | 7.2.14: IntCtl (CP0 Register 12, Select 1): Setup for Interrupt Vector and Interrupt Priority Features |       |

|    | 7.2.15: SRSCtl (CP0 Register12, Select 2): Shadow Register Set Selectors                               |       |

|    | 7.2.16: SRSMap (CP0 Register 12, Select 3): Shadow Set Choice for Each Interrupt Level in VI Mode      |       |

|    | 7.2.17: Cause (CP0 Register 13, Select 0): Cause of Last General Exception                             |       |

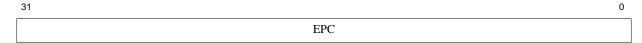

|    | 7.2.18: EPC (CP0 Register 14, Select 0): Restart Address from Exception                                |       |

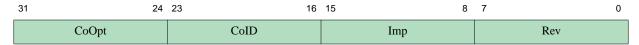

|    | 7.2.19: PRId (CP0 Register 15, Select 0): Processor Identification and Revision                        |       |

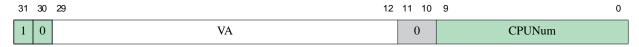

|    | 7.2.20: EBase (CP0 Register 15, Select 1): Exception entry point base address and CPU/VPE ID           |       |

|    | 7.2.21: Config (CP0 Register 16, Select 0): Legacy Configuration Register                              |       |

|    | 7.2.22: Config1-2 (CP0 Register 16, Select 1-2): MIPS32/64 Configuration Registers                     |       |

|    | 7.2.22.1: Config1                                                                                      |       |

|    | 7.2.22.2: Config2                                                                                      |       |

|    | 7.2.23: Config3 (CP0 Register 16, Select 3): Configuration register showing ASEs                       |       |

|    | 7.2.24: Config7 (CP0 Register 16, Select 7): CPU-specific Configuration                                |       |

|    | 7.2.24.1: Config7                                                                                      |       |

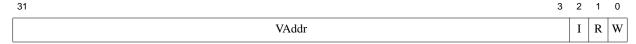

|    | 7.2.25: WatchLo0-3 (CP0 Register 18, Select 0-3): Watchpoint Address and Qualifiers                    |       |

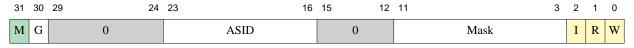

|    | 7.2.26: WatchHi0-3 (CP0 Register 19, Select 0-3): Watchpoint Control/Status                            | . 176 |

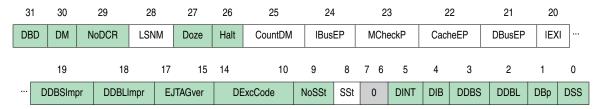

|    | 7.2.27: Debug (CP0 Register 23, Select 0): EJTAG Debug Status/Control                                  |       |

|    | Register                                                                                               | . 1// |

|    | 7.2.28: Trace Control Register (CP0 Register 23, Select 1)                                             |       |

|    | 7.2.29: Trace Control2 Register (CP0 Register 23, Select 2)                                            | . 182 |

|    | 7.2.30: User Trace Data1 Register (CP0 Register 23, Select 3) and User Trace Data2 Register (CP0       | 404   |

|    | Register 24, Select 3)                                                                                 |       |

|    | 7.2.31: TraceBPC Register (CP0 Register 23, Select 4)                                                  |       |

|    | 7.2.32: TraceDBPC Register (CP0 Register 23, Select 5)                                                 |       |

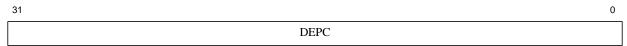

|    | 7.2.33: DEPC (CP0 Register 24, Select 0): Restart Address from Last EJTAG Debug Exception              |       |

|    | 7.2.34: Trace Control3 Register (CP0 Register 24, Select 2)                                            |       |

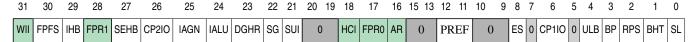

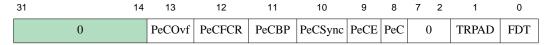

|    | 7.2.35: PerfCtl0-3 (CP0 Register 25, Select 0, 2, 4, 6): Performance Counter Control                   |       |

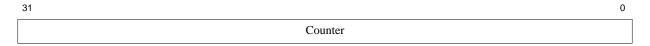

|    | 7.2.36: PerfCnt0-3 (CP0 Register 25, Select 1, 3, 5, 7): Performance Counters                          | . 193 |

| 7.2.37: ErrCtl (CP0 Register 26, Select 0): Software Parity Control and Test Modes for Cacl                                                                                     | he RAM Arrays                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 7.2.38: CacheErr (CP0 Register 27, Select 0): Cache Parity Exception Status                                                                                                     | 105                                         |

| 7.2.39: ITagLo (CP0 Register 28, Select 0): Read/write Interface for Load/Store Tag Cache                                                                                       |                                             |

| 7.2.39.1: ITagLo (ErrCtlWST = 0, ErrCtlSPR = 0)                                                                                                                                 |                                             |

| 7.2.39.2: ITagLo-WST(ErrCtlWST = 1, ErrCtlSPR = 0)                                                                                                                              |                                             |

| 7.2.39.3: ITagLo-WST(ErrCtlWST = 0, ErrCtlSPR = 1)                                                                                                                              |                                             |

| 7.2.40: IDataLo (CP0 Register 28, Select 1): Read/write Interface for I-cache Special Cache                                                                                     |                                             |

| 7.2.41: DTagLo (CP0 Register 28, Select 2): Read/Write Interface for Load/Store Tag Cach                                                                                        |                                             |

| 7.2.41.1: DTagLo (ErrCtlWST = 0, ErrCtlDYT = 0, ErrCtlSPR = 0)                                                                                                                  |                                             |

| 7.2.41.2: DTagLo-WST(ErrCtlWST = 1, ErrCtlDYT = 0, ErrCtlSPR= 0)                                                                                                                |                                             |

| 7.2.41.3: DTagLo-DYT(ErrCtlWST = 0, ErrCtlDYT = 1, ErrCtlSPR) = 0)                                                                                                              |                                             |

| 7.2.41.4: DTagLo-SPT(ErrCtlWST = 0, ErrCtlDYT = 0, ErrCtlSPR) = 1)                                                                                                              |                                             |

| 7.2.42: DDataLo (CP0 Register 28, Select 3): Low-order Data Read/Write Interface for D-ca                                                                                       |                                             |

| 7.2.43: L23TagLo (CP0 Register 28, Select 4): L2 and L3 Cacheop Tag Use                                                                                                         |                                             |

| 7.2.44: L23DataLo (CP0 Register 28, Select 5): Low-order Data Read/Write Interface for L2                                                                                       |                                             |

| 201                                                                                                                                                                             |                                             |

| 7.2.45: ITagHi (CP0 Register 29, Select 0): I-cache Predecode Bits                                                                                                              | 201                                         |

| 7.2.46: IDataHi (CP0 Register 29, Select 1): High-order Data Read/write Interface for I-cach                                                                                    | he Special                                  |

| Cacheops                                                                                                                                                                        | 202                                         |

| 7.2.47: DTagHi (CP0 Register 29, Select 2): D-cache Virtual Index (including ASID)                                                                                              | 202                                         |

| 7.2.48: L23DataHi (CP0 Register 29, Select 5): High-order Data Read/Write Interface for L2                                                                                      |                                             |

| 203                                                                                                                                                                             |                                             |

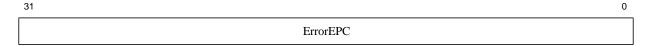

| 7.2.49: ErrorEPC (CP0 Register 30, Select 0): Restart Location from Reset or Cache Error                                                                                        | Exception. 203                              |

| 7.2.50: DESAVE (CP0 Register 31, Select 0): Scratch Read/Write Register for EJTAG Deb                                                                                           |                                             |

| Handler                                                                                                                                                                         | 204                                         |

| Chapter 8: Hardware and Software Initialization of the 74K™ Core                                                                                                                | 205                                         |

| 8.1: Hardware-Initialized Processor State                                                                                                                                       |                                             |

| 8.1.1: Coprocessor 0 State                                                                                                                                                      |                                             |

| 8.1.2: TLB Initialization                                                                                                                                                       |                                             |

| 8.1.3: Bus State Machines                                                                                                                                                       |                                             |

| 8.1.4: Static Configuration Inputs                                                                                                                                              |                                             |

| 8.1.5: Fetch Address                                                                                                                                                            |                                             |

| 8.2: Software-Initialized Processor State                                                                                                                                       |                                             |

| 8.2.1: Register File                                                                                                                                                            | 206                                         |

| 8.2.2: TLB                                                                                                                                                                      | ∠∪0                                         |

| 8.2.3: Caches                                                                                                                                                                   |                                             |

| 8.2.4: Coprocessor 0 State                                                                                                                                                      | 207                                         |

| 0.2.4. Coprocessor o State                                                                                                                                                      | 207<br>207                                  |

| ·                                                                                                                                                                               | 207<br>207<br>207                           |

| Chapter 9: Caches of the 74K™ Core                                                                                                                                              | 207207                                      |

| Chapter 9: Caches of the 74K™ Core<br>9.1: Cache Configurations                                                                                                                 |                                             |

| Chapter 9: Caches of the 74K <sup>™</sup> Core  9.1: Cache Configurations  9.2: Instruction Cache                                                                               |                                             |

| Chapter 9: Caches of the 74K <sup>™</sup> Core  9.1: Cache Configurations  9.2: Instruction Cache  9.2.1: Virtual Aliasing                                                      |                                             |

| Chapter 9: Caches of the 74K <sup>™</sup> Core  9.1: Cache Configurations  9.2: Instruction Cache  9.2.1: Virtual Aliasing  9.2.2: Precode bits                                 |                                             |

| Chapter 9: Caches of the 74K <sup>™</sup> Core  9.1: Cache Configurations  9.2: Instruction Cache  9.2.1: Virtual Aliasing  9.2.2: Precode bits  9.2.3: Parity                  |                                             |

| Chapter 9: Caches of the 74K <sup>™</sup> Core  9.1: Cache Configurations  9.2: Instruction Cache  9.2.1: Virtual Aliasing  9.2.2: Precode bits  9.2.3: Parity  9.3: Data Cache |                                             |

| Chapter 9: Caches of the 74K™ Core  9.1: Cache Configurations  9.2: Instruction Cache                                                                                           |                                             |

| Chapter 9: Caches of the 74K™ Core  9.1: Cache Configurations  9.2: Instruction Cache                                                                                           |                                             |

| Chapter 9: Caches of the 74K™ Core  9.1: Cache Configurations  9.2: Instruction Cache                                                                                           |                                             |

| Chapter 9: Caches of the 74K™ Core  9.1: Cache Configurations  9.2: Instruction Cache                                                                                           | 207 207 209 209 209 210 211 211 212 212 213 |

| O. F. O. Banka annual Balling                                | 045    |

|--------------------------------------------------------------|--------|

| 9.5.3: Replacement Policy                                    |        |

| 9.5.4: Virtual Aliasing                                      |        |

| 9.6: CACHE Instruction                                       |        |

| 9.7: Software Cache Testing                                  |        |

| 9.7.1: I-cache/D-cache Tag Arrays                            |        |

| 9.7.2: I-cache Data Array                                    |        |

| 9.7.3: I-cache WS Array                                      |        |

| 9.7.4: D-Cache Data Array                                    |        |

| 9.7.5: D-cache WS Array<br>9.7.6: D-cache DirtyArray         |        |

| 9.7.6. D-cache DiffyAffay                                    |        |

| 9.6. Memory Conerence issues                                 | 210    |

| Chapter 10: Power Management in the 74K™ Core                | 221    |

| 10.1: Register-Controlled Power Management                   |        |

| 10.2: Instruction-Controlled Power Management                |        |

| 5                                                            |        |

| Chapter 11: EJTAG Debug Support in the 74K™ Core             | 223    |

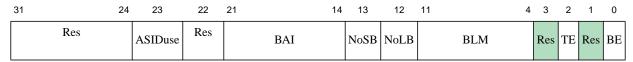

| 11.1: Debug Control Register                                 |        |

| 11.2: Hardware Breakpoints                                   |        |

| 11.2.1: Features of Instruction Breakpoint                   |        |

| 11.2.2: Features of Data Breakpoint                          | 227    |

| 11.2.3: Instruction Breakpoint Registers Overview            | 228    |

| 11.2.4: Data Breakpoint Registers Overview                   | 228    |

| 11.2.5: Conditions for Matching Breakpoints                  | 229    |

| 11.2.5.1: Conditions for Matching Instruction Breakpoints    | 229    |

| 11.2.5.2: Conditions for Matching Data Breakpoints           | 229    |

| 11.2.6: Debug Exceptions from Breakpoints                    | 230    |

| 11.2.6.1: Debug Exception by Instruction Breakpoint          | 230    |

| 11.2.6.2: Debug Exception by Data Breakpoint                 | 231    |

| 11.2.7: Breakpoint used as TriggerPoint                      | 232    |

| 11.2.8: Instruction Breakpoint Registers                     |        |

| 11.2.8.1: Instruction Breakpoint Status (IBS) Register       | 233    |

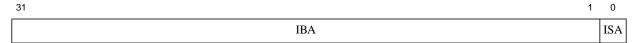

| 11.2.8.2: Instruction Breakpoint Address n (IBAn) Register   | 233    |

| 11.2.8.3: Instruction Breakpoint Address Mask n (IBMn) Regis | ter234 |

| 11.2.8.4: Instruction Breakpoint ASID n (IBASIDn) Register   |        |

| 11.2.8.5: Instruction Breakpoint Control n (IBCn) Register   |        |

| 11.2.9: Data Breakpoint Registers                            |        |

| 11.2.9.1: Data Breakpoint Status (DBS) Register              |        |

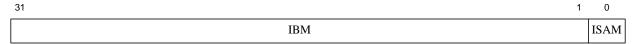

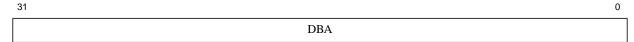

| 11.2.9.2: Data Breakpoint Address n (DBAn) Register          |        |

| 11.2.9.3: Data Breakpoint Address Mask n (DBMn) Register     |        |

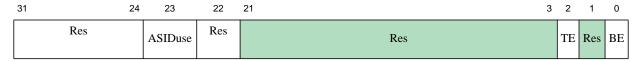

| 11.2.9.4: Data Breakpoint ASID n (DBASIDn) Register          |        |

| 11.2.9.5: Data Breakpoint Control n (DBCn) Register          |        |

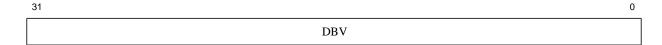

| 11.2.9.6: Data Breakpoint Value n (DBVn) Register            |        |

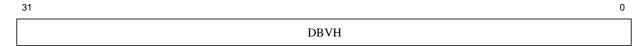

| 11.2.9.7: Data Breakpoint Value High n (DBVHn) Register      |        |

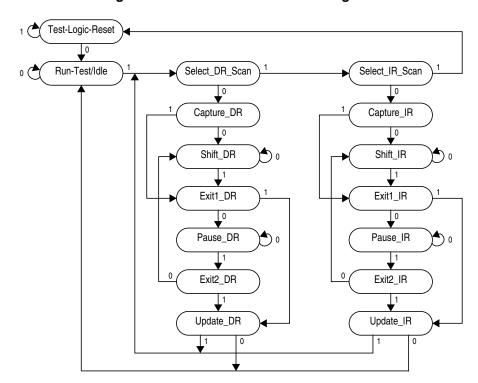

| 11.3: Test Access Port (TAP)                                 |        |

| 11.3.1: EJTAG Internal and External Interfaces               |        |

| 11.3.2: Test Access Port Operation                           |        |

| 11.3.2.1: Test-Logic-Reset State                             |        |

| 11.3.2.2: Run-Test/Idle State                                |        |

| 11.3.2.3: Select_DR_Scan State                               |        |

| 11.3.2.4: Select_IR_Scan State                               |        |

| 11.3.2.5: Capture_DR State                                   |        |

| 11.3.2.6: Shift DR State                                     | 243    |

| 11.3.2.7: Exit1_DR State                                           | 243 |

|--------------------------------------------------------------------|-----|

| 11.3.2.8: Pause_DR State                                           | 243 |

| 11.3.2.9: Exit2_DR State                                           | 243 |

| 11.3.2.10: Update_DR State                                         |     |

| 11.3.2.11: Capture_IR State                                        |     |

| 11.3.2.12: Shift_IR State                                          |     |

| 11.3.2.13: Exit1_IR State                                          |     |

| 11.3.2.14: Pause_IR State                                          |     |

| 11.3.2.15: Exit2_IR State                                          |     |

| 11.3.2.16: Update_IR State                                         |     |

| 11.3.3: Test Access Port (TAP) Instructions                        |     |

| 11.3.3.1: BYPASS Instruction                                       |     |

| 11.3.3.2: IDCODE Instruction                                       |     |

| 11.3.3.3: IMPCODE Instruction                                      |     |

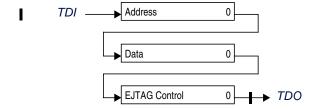

| 11.3.3.4: ADDRESS Instruction                                      |     |

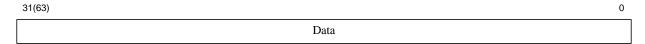

| 11.3.3.5: DATA Instruction                                         |     |

|                                                                    |     |

| 11.3.3.6: CONTROL Instruction                                      |     |

| 11.3.3.7: ALL Instruction                                          |     |

| 11.3.3.8: EJTAGBOOT Instruction                                    |     |

| 11.3.3.9: NORMALBOOT Instruction                                   |     |

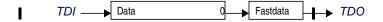

| 11.3.3.10: FASTDATA Instruction                                    |     |

| 11.3.3.11: TCBCONTROLA Instruction                                 |     |

| 11.3.3.12: TCBCONTROLB Instruction                                 |     |

| 11.3.3.13: TCBCONTROLC Instruction                                 |     |

| 11.3.3.14: TCBCONTROLE Instruction                                 |     |

| 11.3.3.15: TCBDATA Instruction                                     |     |

| 11.3.3.16: PCSAMPLE Instruction                                    |     |

| 11.4: EJTAG TAP Registers                                          |     |

| 11.4.1: Instruction Register                                       |     |

| 11.4.2: Data Registers Overview                                    |     |

| 11.4.2.1: Bypass Register                                          |     |

| 11.4.2.2: Device Identification (ID) Register                      |     |

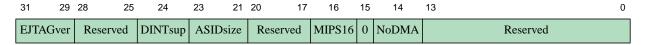

| 11.4.2.3: Implementation Register                                  | 249 |

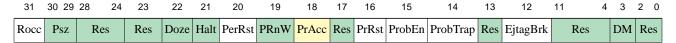

| 11.4.2.4: EJTAG Control Register                                   | 250 |

| 11.4.3: Processor Access Address Register                          | 254 |

| 11.4.3.1: Processor Access Data Register                           | 254 |

| 11.4.4: Fastdata Register (TAP Instruction FASTDATA)               | 255 |

| 11.5: TAP Processor Accesses                                       | 256 |

| 11.5.1: Fetch/Load and Store From/To the EJTAG Probe Through dmseg | 256 |

| 11.6: PC Sampling                                                  | 258 |

| 11.6.1: PC Sampling in Wait State                                  |     |

| 11.7: MIPS® Trace                                                  |     |

| 11.7.1: Processor Modes                                            |     |

| 11.7.2: Software Versus Hardware Control                           |     |

| 11.7.3: Trace Information                                          |     |

| 11.7.4: Load/Store Address and Data Trace Information              |     |

| 11.7.5: Programmable Processor Trace Mode Options                  |     |

| 11.7.6: Programmable Trace Information Options                     |     |

| 11.7.6.1: User Data Trace                                          |     |

| 11.7.7: Enable Trace to Probe On-chip Memory                       |     |

| 11.7.8: TCB Trigger                                                |     |

| 11.7.9: Cycle-by-Cycle Information                                 |     |

| 11.7.10: Instruction and Data Cache Miss Tracing                   |     |

| TT. / TO, INSTRUCTION AND DATA CACHE WISS TRACING                  | ∠03 |

| 11.7.11: Performance Counter Tracing                                    | 263 |

|-------------------------------------------------------------------------|-----|

| 11.7.12: Filtered Data Trace Mode                                       | 264 |

| 11.7.13: PC tracing off                                                 | 264 |

| 11.7.14: TMOAS Handling                                                 |     |

| 11.7.15: Memory-mapped Access to On-Chip Trace RAM                      |     |

| 11.7.16: Core-Specific Event Inefficiency Tracing                       |     |

| 11.7.17: Trace Message Format                                           |     |

| 11.7.18: Trace Word Format                                              |     |

| 11.8: PDtrace™ Registers (Software Control)                             |     |

| 11.9: Trace Control Block (TCB) Registers (Hardware Control)            |     |

| 11.9.1: TCBCONTROLA Register                                            |     |

| 11.9.2: TCBCONTROLA Register                                            |     |

| 11.9.3: TCBDATA Register                                                |     |

| 11.9.4: TCBCONTROLC Register                                            |     |

| 11.9.5: TCBCONTROLE Register                                            |     |

| · · · · · · · · · · · · · · · · · · ·                                   |     |

| 11.9.6: TCBCONFIG Register (Reg 0)                                      |     |

|                                                                         |     |

| 11.9.8: TCBRDP Register (Reg 5)                                         |     |

| 11.9.9: TCBWRP Register (Reg 6)                                         |     |

| 11.9.10: TCBSTP Register (Reg 7)                                        |     |

| 11.9.11: TCBTRIGx Register (Reg 16-23)                                  |     |

| 11.9.12: Register Reset State                                           |     |

| 11.10: Enabling MIPS Trace                                              |     |

| 11.10.1: Trace Trigger from EJTAG Hardware Instruction/Data Breakpoints |     |

| 11.10.2: Turning On PDtrace™ Trace                                      |     |

| 11.10.3: Turning Off PDtrace™ Trace                                     |     |

| 11.10.4: TCB Trace Enabling                                             |     |

| 11.10.5: Tracing a Reset Exception                                      |     |

| 11.11: TCB Trigger Logic                                                |     |

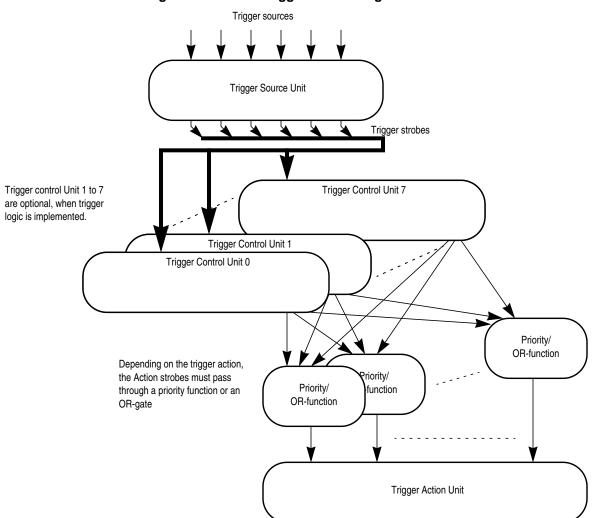

| 11.11.1: Trigger Units Overview                                         |     |

| 11.11.2: Trigger Source Unit                                            |     |

| 11.11.3: Trigger Control Units                                          |     |

| 11.11.4: Trigger Action Unit                                            |     |

| 11.11.5: Simultaneous Triggers                                          |     |

| 11.11.5.1: Prioritized Trigger Actions                                  |     |

| 11.11.5.2: OR'ed Trigger Actions                                        |     |

| 11.12: MIPS Trace Cycle-by-Cycle Behavior                               |     |

| 11.12.1: FIFO Logic in PDtrace and TCB Modules                          |     |

| 11.12.2: Handling of FIFO Overflow in the PDtrace Module                |     |

| 11.12.3: Handling of FIFO Overflow in the TCB                           |     |

| 11.12.3.1: Probe Width and Clock-ratio Settings                         |     |

| 11.12.4: Adding Cycle Accurate Information to the Trace                 |     |

| 11.13: TCB On-Chip Trace Memory                                         |     |

| 11.13.1: On-Chip Trace Memory Size                                      |     |

| 11.13.2: Trace-From Mode                                                |     |

| 11.13.3: Trace-To Mode                                                  | 296 |

| Chapter 12: Instruction Set Overview                                    |     |

| 12.1: CPU Instruction Formats                                           |     |

| 12.2: Load and Store Instructions                                       |     |

| 12.2.1: Scheduling a Load Delay Slot                                    |     |

| 12.2.2: Defining Access Types                                           | 298 |

| 12.3: Computational Instructions                                        | 299 |

| Appendix B: Revision History                                                       | 351 |

|------------------------------------------------------------------------------------|-----|

| Appendix A: References                                                             | 349 |

|                                                                                    |     |

| 14.2: Instruction Listing                                                          | 345 |

| 14.1: Instruction Bit Encoding                                                     |     |

| Chapter 14: MIPS16e™ Application-Specific Extension to the MIPS32® Instruction Set | 343 |

|                                                                                    |     |

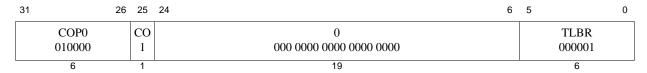

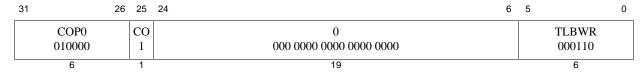

| TLBWR                                                                              |     |

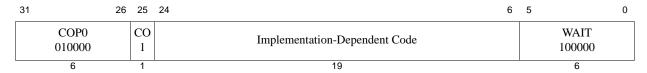

| WAIT                                                                               |     |

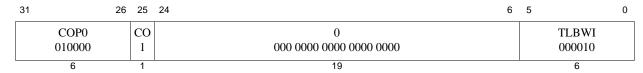

| TLBWI                                                                              |     |

| TLBR                                                                               |     |

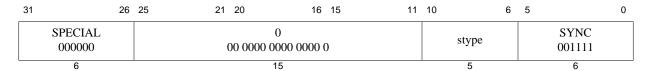

| SYNC                                                                               |     |

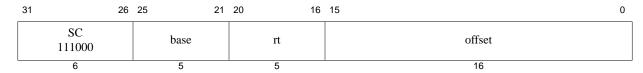

| SC                                                                                 |     |

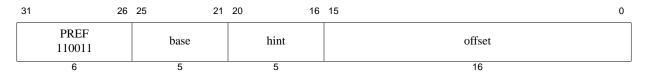

| PREF                                                                               |     |

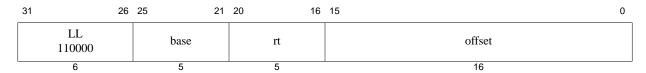

| LL                                                                                 |     |

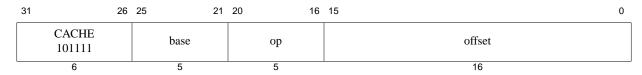

| CACHE                                                                              |     |

| 13.3: Floating Point Unit Instruction Format Encodings                             |     |

| 13.2: 74K™ Opcode Map                                                              |     |

| 13.1: Understanding the Instruction Descriptions                                   |     |

| Chapter 13: 74K™ Processor Core Instructions                                       |     |

|                                                                                    |     |

| 12.6: Coprocessor Instructions                                                     | 301 |

| 12.5: Control Instructions                                                         |     |

| 12.4.2: Overview of Branch Instructions                                            |     |

| 12.4.1: Overview of Jump Instructions                                              |     |

| 12.4: Jump and Branch Instructions                                                 |     |

| 12.3.1: Cycle Timing for Multiply and Divide Instructions                          | 300 |

# **List of Figures**

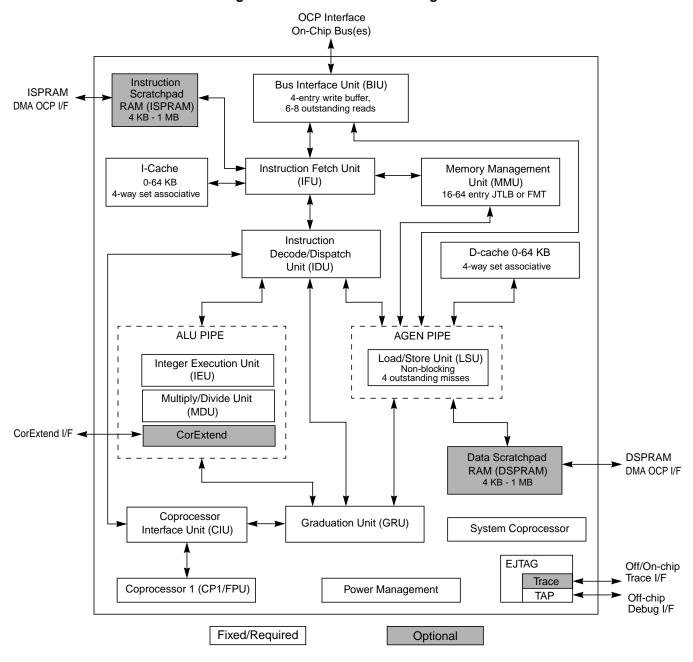

| Figure 1.1: 74K™ Core Block Diagram                                               | 29  |

|-----------------------------------------------------------------------------------|-----|

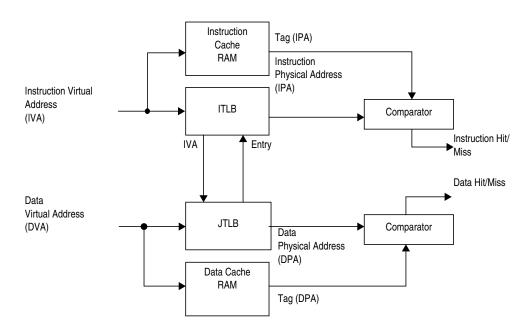

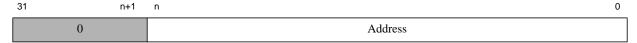

| Figure 1.2: Address Translation During a Cache Access                             |     |

| Figure 2.1: 74K™ Core Pipeline                                                    | 38  |

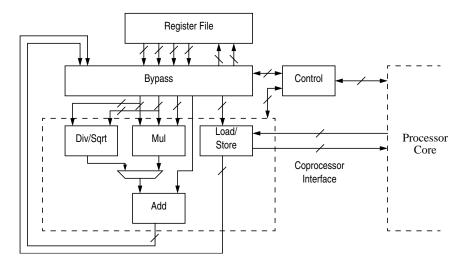

| Figure 3.1: FPU Block Diagram                                                     |     |

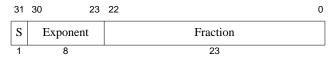

| Figure 3.2: Single-Precision Floating-Point Format (S)                            | 52  |

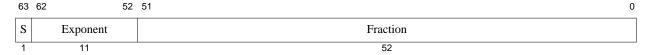

| Figure 3.3: Double-Precision Floating-Point Format (D)                            | 52  |

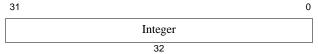

| Figure 3.4: Word Fixed-Point Format (W)                                           | 54  |

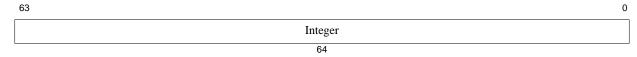

| Figure 3.5: Longword Fixed-Point Format (L)                                       |     |

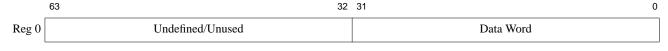

| Figure 3.6: Single Floating-Point or Word Fixed-Point Operand in an FPR           | 55  |

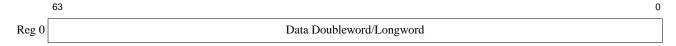

| Figure 3.7: Double Floating-Point or Longword Fixed-Point Operand in an FPR       |     |

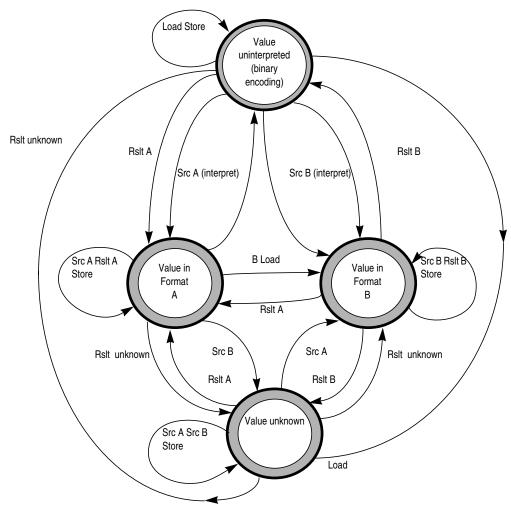

| Figure 3.8: Effect of FPU Operations on the Format of Values Held in FPRs         |     |

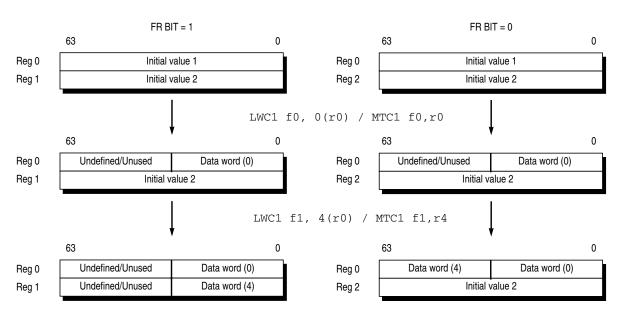

| Figure 3.9: FPU Word Load and Move-to Operations                                  |     |

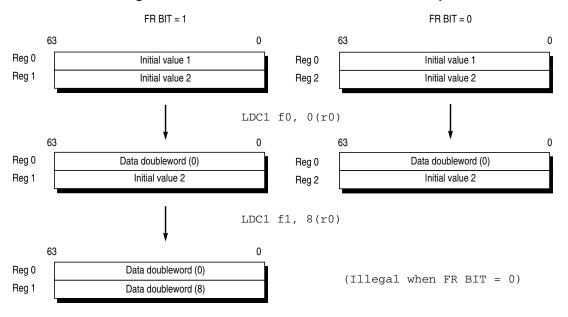

| Figure 3.10: FPU Doubleword Load and Move-to Operations                           |     |

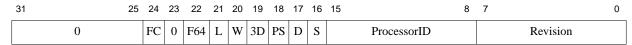

| Figure 3.11: FIR Format                                                           |     |

| Figure 3.12: FCCR Format                                                          |     |

| Figure 3.13: FEXR Format                                                          |     |

| Figure 3.14: FENR Format                                                          |     |

| Figure 3.15: FCSR Format                                                          |     |

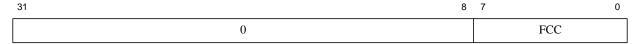

| Figure 3.16: FS/FO/FN Bits Influence on Multiply and Addition Results             |     |

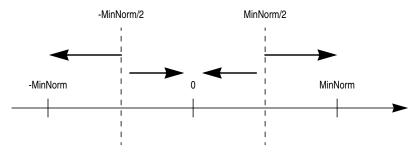

| Figure 3.17: Flushing to Nearest when Rounding Mode is Round to Nearest           |     |

| Figure 3.18: FPU Pipeline                                                         |     |

| Figure 3.19: Arithmetic Pipeline Bypass Paths                                     |     |

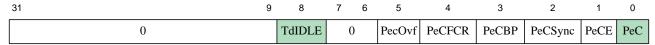

| Figure 4.1: MIPS32® DSP ASE Control Register (DSPControl) Format                  |     |

| Figure 5.1: Address Translation For Cache Access with TLB MMU                     |     |

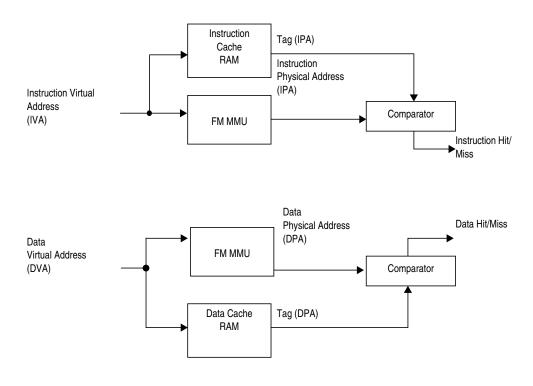

| Figure 5.2: Address Translation For Cache Access with FM MMU                      |     |

| Figure 5.3: 74K™ Processor Core Virtual Memory Map                                |     |

| Figure 5.4: User Mode Virtual Address Space                                       |     |

| Figure 5.5: Supervisor Mode Virtual Address Space                                 |     |

| Figure 5.6: Kernel Mode Virtual Address Space                                     |     |

| Figure 5.7: Debug Mode Virtual Address Space                                      |     |

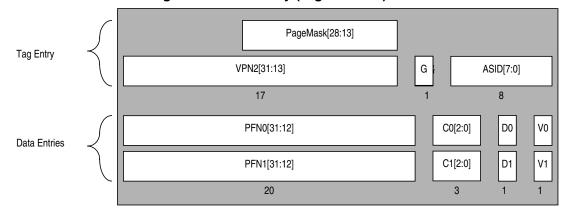

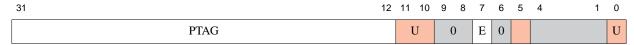

| Figure 5.8: JTLB Entry (Tag and Data)                                             |     |

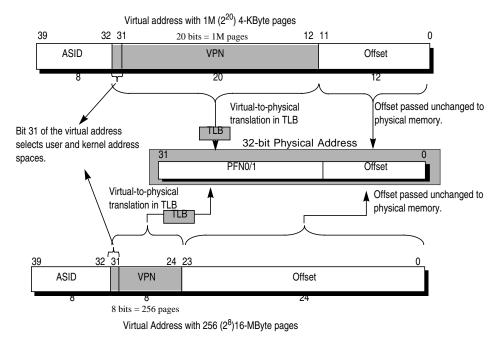

| Figure 5.9: Overview of Virtual-to-Physical Address Translation                   | 100 |

| Figure 5.10: 32-bit Virtual Address Translation                                   |     |

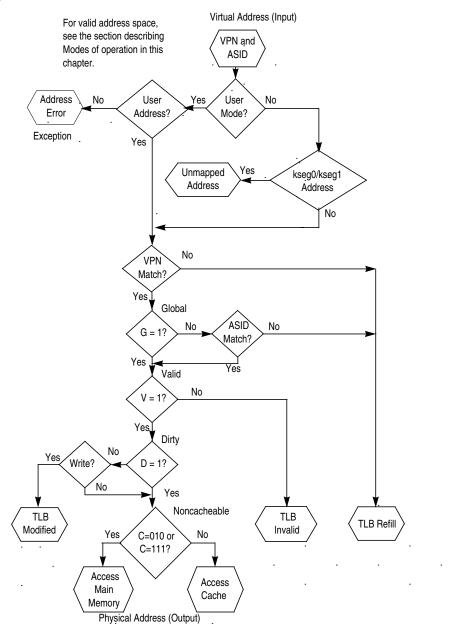

| Figure 5.11: TLB Address Translation Flow in the 74K™ Processor Core              |     |

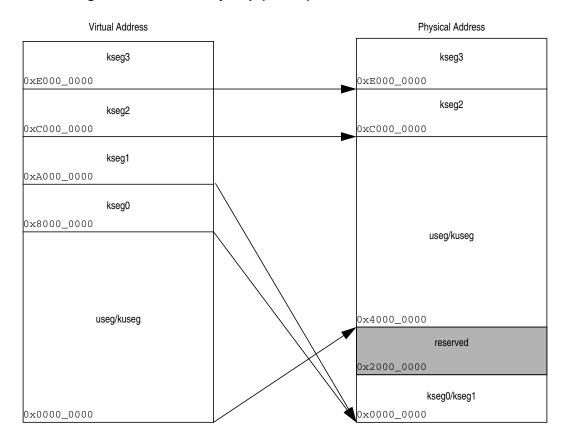

| Figure 5.12: FM Memory Map (ERL=0) in the 74K™ Processor Core                     |     |

| Figure 5.13: FM Memory Map (ERL=1) in the 74K <sup>™</sup> Processor Core         |     |

| Figure 6.1: Interrupt Generation for Vectored Interrupt Mode                      | 113 |

| Figure 6.2: Interrupt Generation for External Interrupt Controller Interrupt Mode |     |

| Figure 6.3: General Exception Handler (HW)                                        |     |

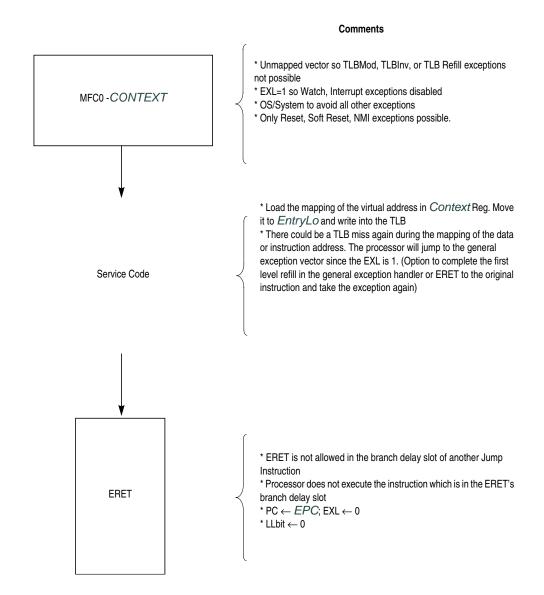

| Figure 6.4: General Exception Servicing Guidelines (SW)                           |     |

| Figure 6.5: TLB Miss Exception Handler (HW)                                       |     |

| Figure 6.6: TLB Exception Servicing Guidelines (SW)                               |     |

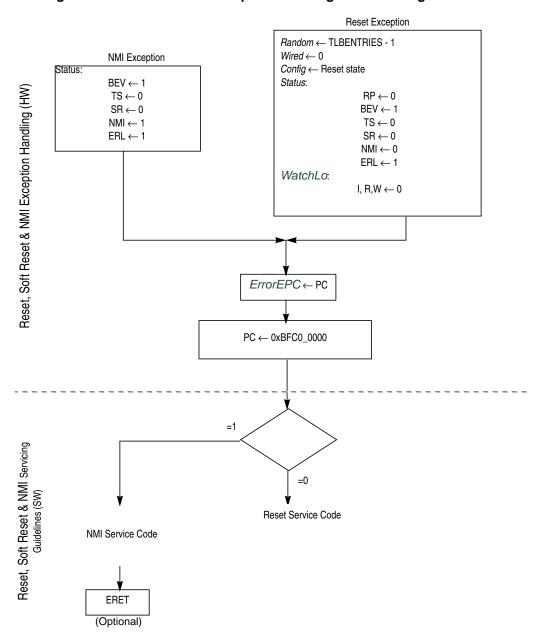

| Figure 6.7: Reset and NMI Exception Handling and Servicing Guidelines             |     |

| Figure 7.1: Register Format Color Coding of Access Field Types                    |     |

| Figure 7.2: Index Register Format                                                 |     |

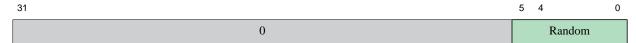

| Figure 7.3: Random Register Format                                                |     |

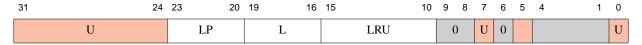

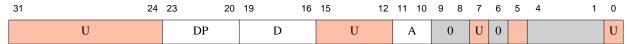

| Figure 7.4: Entryl of Entryl of Register Format                                   | 149 |

| Figure 7.5: Context Register Format                                                | 151 |

|------------------------------------------------------------------------------------|-----|

| Figure 7.6: IUserLocal Register Format                                             |     |

| Figure 7.7: PageMask Register Format                                               | 153 |

| Figure 7.8: Wired Register Format                                                  | 154 |

| Figure 7.9: HWREna Register Format                                                 | 154 |

| Figure 7.10: BadVAddr Register Format                                              | 155 |

| Figure 7.11: Count Register Format                                                 |     |

| Figure 7.12: EntryHi Register Format                                               |     |

| Figure 7.13: Compare Register Format                                               |     |

| Figure 7.14: Status Register Format                                                |     |

| Figure 7.15: IntCtl Register Format                                                |     |

| Figure 7.16: SRSCtl Register Format                                                |     |

| Figure 7.17: SRSMap Register Format                                                |     |

| Figure 7.18: Cause Register Format                                                 |     |

| Figure 7.19: EPC Register Format                                                   |     |

| Figure 7.79. Et & Register Format                                                  | 167 |

| Figure 7.20: Fixed Register Format                                                 |     |

| Figure 7.21: Ebase Register Format                                                 |     |

| Figure 7.23: Config1 Register Format                                               | 170 |

| Figure 7.23. Config2 Register Format                                               | 170 |

| Figure 7.24. Cornig2 Register Forma                                                | 171 |

| Figure 7.25. Cornigs Register Format                                               | 172 |

|                                                                                    |     |

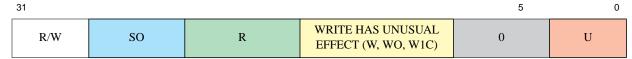

| Figure 7.27: WatchLo Register FormatFigure 7.28: WatchHi Register Format           |     |

|                                                                                    |     |

| Figure 7.29: Debug Register Format                                                 |     |

| Figure 7.30: TraceControl Register Format                                          |     |

| Figure 7.31: TraceControl2 Register Format                                         |     |

| Figure 7.32: User Trace Data1 / User Trace Data2 Register Format                   |     |

| Figure 7.33: TraceBPC Register Format                                              |     |

| Figure 7.34: TraceDBPC Register Format                                             |     |

| Figure 7.35: DEPC Register Format                                                  |     |

| Figure 7.36: TraceControl3 Register Format                                         |     |

| Figure 7.37: PerfCtl0-3 Register Format                                            |     |

| Figure 7.38: Performance Counter Count Register                                    |     |

| Figure 7.39: CacheErr Register Format                                              |     |

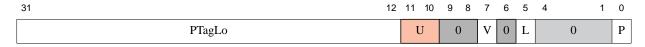

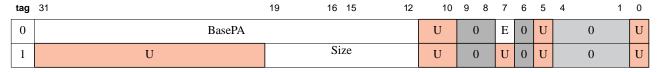

| Figure 7.40: ITagLo Register Format (ErrCtlWST = 0, ErrCtlSPR = 0)                 |     |

| Figure 7.41: ITagLo Register Format (ErrCtlWST = 1, ErrCtlSPR = 0)                 |     |

|                                                                                    | 197 |

| Figure 7.43: IDataLo Register Format                                               |     |

| Figure 7.44: DTagLo Register Format (ErrCtlWST = 0, ErrCtlDYT = 0, ErrCtlSPR = 0)  |     |

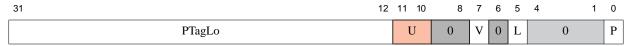

| Figure 7.45: DTagLo Register Format (ErrCtlWST = 1, ErrCtlDYT = 0, ErrCtlSPR = 0)  |     |

| Figure 7.46: Field Descriptions for DTagLo-DYT Register                            |     |

| Figure 7.47: DTagLo Register Format (ErrCtlWST = 0, ErrCtlDYT = 0, ErrCtlSPR) = 1) |     |

| Figure 7.48: DDataLo Register Format                                               |     |

| Figure 7.49: L23TagLo Register Format                                              |     |

| Figure 7.50: L23DataLo Register Format                                             | 201 |

| Figure 7.51: ITagHi Register Format                                                |     |

| Figure 7.52: IDataHi Register Format                                               |     |

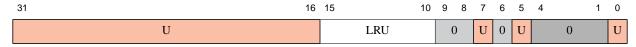

| Figure 7.53: DTagHi Register Format                                                | 202 |

| Figure 7.54: L23DataHi Register Format                                             |     |

| Figure 7.55: ErrorEPC Register Format                                              |     |

| Figure 7.56: DeSave Register Format                                                | 204 |

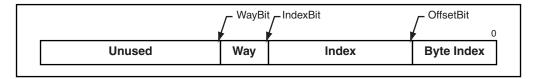

| Figure 9.1: Instruction Cache Organization                                         | 210 |

| Figure 9.2: Data Cache Organization                                                       | 212 |

|-------------------------------------------------------------------------------------------|-----|

| Figure 11.1: Debug Control Register                                                       | 224 |

| Figure 11.2: IBS Register Format                                                          | 233 |

| Figure 11.3: IBAn Register Format                                                         | 234 |

| Figure 11.4: IBMn Register Format                                                         | 234 |

| Figure 11.5: IBASIDn Register Format                                                      | 235 |

| Figure 11.6: IBCn Register Format                                                         | 235 |

| Figure 11.7: DBS Register Format                                                          |     |

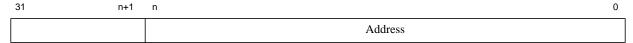

| Figure 11.8: DBAn Register Format                                                         | 237 |

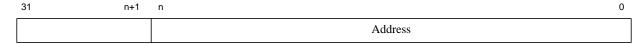

| Figure 11.9: DBMn Register Format                                                         | 237 |

| Figure 11.10: DBASIDn Register Format                                                     | 238 |

| Figure 11.11: DBCn Register Format                                                        | 238 |

| Figure 11.12: DBVn Register Format                                                        | 239 |

| Figure 11.13: DBVHn Register Format                                                       | 240 |

| Figure 11.14: TAP Controller State Diagram                                                |     |

| Figure 11.15: Concatenation of the EJTAG Address, Data and Control Registers              |     |

| Figure 11.16: TDI to TDO Path When in Shift-DR State and FASTDATA Instruction is Selected | 247 |

| Figure 11.17: Device Identification Register Format                                       | 249 |

| Figure 11.18: Implementation Register Format                                              | 249 |

| Figure 11.19: EJTAG Control Register Format                                               |     |

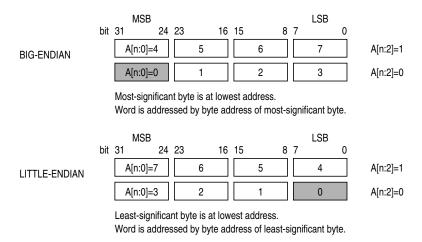

| Figure 11.20: Endian Formats for PAD Register                                             |     |

| Figure 11.21: Fastdata Register Format                                                    |     |

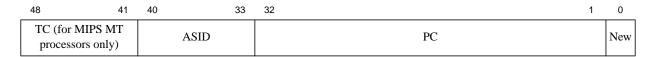

| Figure 11.22: TAP Register PCsample Format                                                |     |

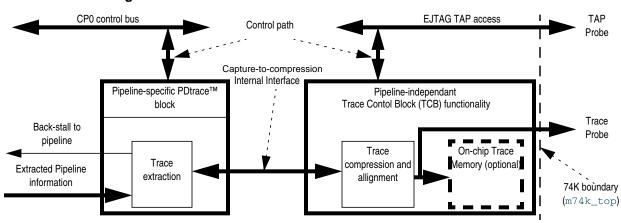

| Figure 11.23: MIPS® Trace Functional Blocks in the 74K™ Core                              |     |

| Figure 11.24: A TMOAS Trace Record                                                        |     |

| Figure 11.25: TCBCONTROLA Register Format                                                 |     |

| Figure 11.26: TCBCONTROLB Register Format                                                 |     |

| Figure 11.27: TCBDATA Register Format                                                     |     |

| Figure 11.28: TCBCONTROLC Register Format                                                 |     |

| Figure 11.29: TCBCONTROLE Register Format                                                 |     |

| Figure 11.30: TCBCONFIG Register Format                                                   |     |

| Figure 11.31: TCBTW Register Format                                                       |     |

| Figure 11.32: TCBRDP Register Format                                                      |     |

| Figure 11.33: TCBWRP Register Format                                                      |     |

| Figure 11.34: TCBSTP Register Format                                                      |     |

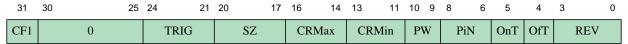

| Figure 11.35: TCBTRIGx Register Format                                                    |     |

| Figure 11.36: TCB Trigger Processing Overview                                             |     |

| Figure 12.1: Instruction Formats                                                          | 298 |

| Figure 13.1: Usage of Address Fields to Select Index and Way                              | 317 |

# **List of Tables**

| Table 2.1: 74K™ Core Pipeline Stages Descriptions                                            | 38 |

|----------------------------------------------------------------------------------------------|----|

| Table 2.2: Execution Hazards                                                                 | 45 |

| Table 2.3: Instruction Hazards                                                               |    |

| Table 2.4: Hazard Instruction Listing                                                        |    |

| Table 3.1: Parameters of Floating-Point Data Types                                           | 51 |

| Table 3.2: Value of Single or Double Floating-Point Data Type Encoding                       |    |

| Table 3.3: Value Supplied When a New Quiet NaN is Created                                    |    |

| Table 3.4: Coprocessor 1 Register Summary                                                    |    |

| Table 3.5: Read/Write Properties                                                             |    |

| Table 3.6: FIR Bit Field Descriptions                                                        |    |

| Table 3.7: FCCR Bit Field Descriptions                                                       |    |

| Table 3.8: FEXR Bit Field Descriptions                                                       |    |

| Table 3.9: FENR Bit Field Descriptions                                                       |    |

| Table 3.10: FCSR Bit Field Descriptions                                                      |    |

| Table 3.11: Cause, Enables, and Flags Definitions                                            |    |

| Table 3.12: Rounding Mode Definitions                                                        | 64 |

| Table 3.13: Handling Denormalized Floating-point Numbers                                     |    |

| Table 3.14: Zero Flushing for Tiny Results                                                   |    |

| Table 3.15: Handling of Denormalized Operand Values and Tiny Results Based on FS Bit Setting |    |

| Table 3.16: Handling of Tiny Intermediate Result Based on the FO and FS Bit Settings         |    |

| Table 3.17: Handling of Tiny Final Result Based on FN and FS Bit Settings                    |    |

| Table 3.18: Recommended FS/FO/FN Settings                                                    |    |

| Table 3.19: FPU Data Transfer Instructions                                                   |    |

| Table 3.20: FPU Loads and Stores Using Register+Offset Address Mode                          |    |

| Table 3.21: FPU Loads and Stores Using Register+Register Address Mode                        |    |

| Table 3.22: FPU Move To and From Instructions                                                |    |

| Table 3.23: FPU IEEE Arithmetic Operations                                                   |    |

| Table 3.24: FPU-Approximate Arithmetic Operations                                            |    |

| Table 3.25: FPU Multiply-Accumulate Arithmetic Operations                                    |    |

| Table 3.26: FPU Conversion Operations Using the FCSR Rounding Mode                           |    |

| Table 3.27: FPU Conversion Operations Using a Directed Rounding Mode                         |    |

| Table 3.29: FPU Conditional Move on True/False Instructions                                  |    |

| Table 3.30: FPU Conditional Move on Zero/Non-Zero Instructions                               |    |

| Table 3.31: FPU Conditional Branch Instructions                                              |    |

| Table 3.32: Deprecated FPU Conditional Branch Likely Instructions                            |    |

| Table 3.33: CPU Conditional Move on FPU True/False Instructions                              |    |

| Table 3.34: Result for Exceptions Not Trapped                                                |    |

| Table 3.35: 74Kf Core FPU Latency and Repeat Rate                                            |    |

| Table 4.1: MIPS® DSP ASE Control Register (DSPControl) Field Descriptions                    |    |

| Table 4.2: DSPControl ouflag Bits                                                            |    |

| Table 5.1: User Mode Segments                                                                |    |

| Table 5.1: Oser Mode Segments                                                                |    |

| Table 5.2: Supervisor Mode Segments                                                          |    |

| Table 5.4: Physical Address and Cache Attributes for dseg, dmseg, and drseg                  |    |

| Table 5.5: CPU Access to drseg                                                               |    |

| Table 5.6: CPU Access to dmseg                                                               |    |

|                                                                                              |    |

| Table 5.7: TLB Tag Entry Fields                                      |     |

|----------------------------------------------------------------------|-----|

| Table 5.8: TLB Data Entry Fields                                     |     |

| Table 5.9: Machine Check Exception                                   | 102 |

| Table 5.10: TLB Instructions                                         |     |

| Table 5.11: Cache Coherency Attributes                               |     |

| Table 5.12: Cacheability of Segments with Fixed Mapping Translation  | 104 |

| Table 6.1: Priority of Exceptions                                    | 108 |

| Table 6.2: Interrupt Modes                                           | 110 |

| Table 6.3: Relative Interrupt Priority for Vectored Interrupt Mode   | 113 |

| Table 6.4: Exception Vector Offsets for Vectored Interrupts          | 117 |

| Table 6.5: Exception Vector Base Addresses, SI_UseExceptionBase = 0  | 119 |

| Table 6.6: Exception Vector Base Addresses, SI_UseExceptionBase = 1  | 120 |

| Table 6.7: Exception Vector Offsets                                  | 120 |

| Table 6.8: Exception Vectors                                         | 121 |

| Table 6.9: Value Stored in EPC, ErrorEPC, or DEPC on Exception       | 122 |